# **Speculatively Granting Conflicting Accesses** on Hardware Transactional Memory

Tomoki Tajimi\*, Yuki Futamase\*,

Thr 1

Tx.Y

Masaki Hayashi\*,

will not violate Isolation.

BEGIN TRANSACTION(0);

COMMIT TRANSACTION(0);

count++;

switch(op){

case 0:

case 1:

case 2:

case 3:

}

Ryota Shioya<sup>+</sup>, Masahiro Goshima<sup>‡</sup>, Tomoaki Tsumura<sup>\*</sup>

\*Nagoya Institute of Technology, <sup>†</sup>The University of Tokyo, <sup>‡</sup>National Institute of Informatics

### Hardware Transactional Memory (HTM)

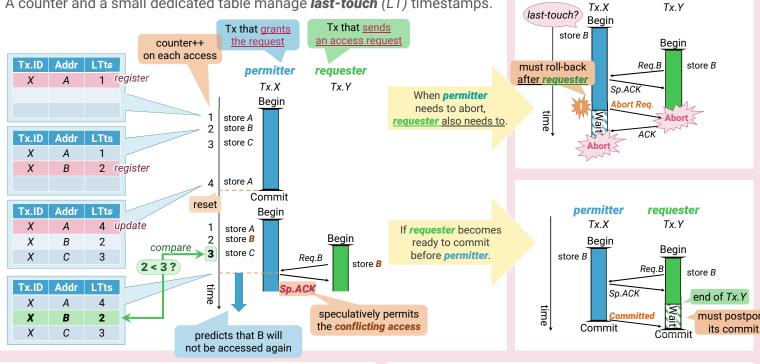

Conflicting Accesses that can be Granted After the *last-touch* of a shared variable.

accesses to the variable by other concurrent Tx

enqueue right();

dequeue\_right();

enqueue left();

dequeue\_left();

Simplified code of Deque

last-touch

of "count

never accessed

again

until its commit

break;

break;

break;

break;

requester

permitter

- Transactions (Tx) are speculatively Thr.0 executed in parallel. Tx.X

- HTM guarantees two properties for Tx.

#### > Atomicity

- Each Tx must not be executed partially.

- Isolation

- The result of concurrently executed Tx must be same as sequentially executed.

Accesses that can violate them are detected as conflicting accesses

### **Granting a Conflicting Access**

• A counter and a small dedicated table manage *last-touch* (*LT*) timestamps.

time

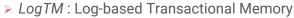

# **Performance Evaluation**

**Simulation** (16 threads)

Simics : Full system simulator (SPARC-V9, Solaris10)

# Hardware Cost

- Dedicated table

- 42bit per one address

Total: 77.1KByte

(per one thread)

max # of access destination addresses per Tx: 15,018

can be reduced by managing

only limited addresses

Each thread manages its permitter and requester 16bit + 16bit (16 threads)

Future Work

- Examine the trade-off between storage capacity and performance

- Evaluation with a large variety of programs

- Detailed area cost estimation